Describe How the Processor Using the First Four Registers Listed

Output Flag 1 bit. The following registers are contained in the processor and connected directly to the system bus.

Different Classes Of Cpu Registers Geeksforgeeks

Input Register 8 bits OUTR.

. Interrupt Enable 1 bit. Output Flag 1 bit. The size of a register usually depends on the CPU type.

The following registers are contained in the CPU and connected directly to the system bus. The following registers are contained in the CPU and connected directly to the systembus. Output Register 8 bits FGI.

Output Register 8 bits FGI. Output flag 1 bit IEN. B the processor checks if there is an interrupt.

Output Register 8 bits. Input Register 8 bits OUTR. Output Flag 1 bit.

Describe how the processor using the first four registers listed in the problem can achieve IO with the teletype. Input Flag 1 bit. Output Register 8 bits FGI.

Registers in the central processing unit are compact fast data storage spaces that are used to temporarily store information for a number of purposes CPU. Input register 8 bits OUTR. The following registers are contained in the processor and connected directly to the system bus.

Output Register 8 bits. IO CPU IO CPU Job2. When there are 4 jobs the CPU is round-robin among the four as is the IO.

A the address of the Interrupt Service Routine ISR is loaded to the Program Counter PC. Input Flag 1 bit. Input Flag 1 bit.

The Intel 8088 CPU. Input Flag 1 bit FGO. Output Register 8 bits FGI.

Input Register 8 bits OUTR. C when the ISR completes the processor restores the register contents. Output Flag 1 bit.

The following registers are contained in the CPU and connected directly to the system bus. When effective access time is 15 ns. A brief description of most important CPUs registers and their functions are given below.

Interrupt Enable 1 bit. Input Flag 1 bit FGO. The hit ratio needed to register the level is 096.

Output Register 8 bits. This register holds the address of memory where CPU wants to read or write data. Consider a computer systemthat contains an IO module controlling a simple keyboardprinter teletype.

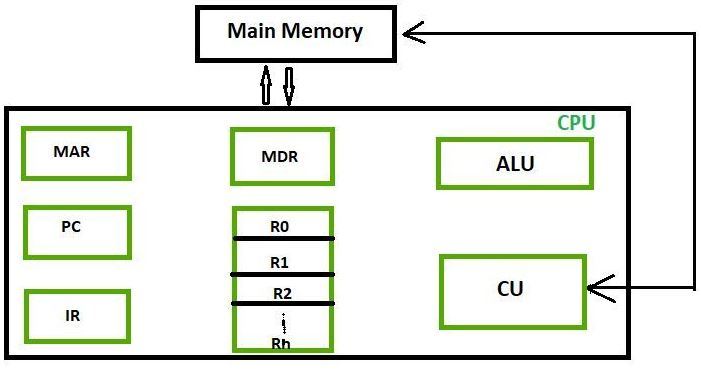

Memory Address Register MAR. These are numbered as R0 R1 R2Rn-1 and used to store temporary data during any ongoing operation. General Purpose Registers.

Interrupt Enable 1 bit Keystroke input from the teletype and printer output to the teletype are controlled by the IO module. Registers are the most important components of CPU. IO CPU IO CPU Job4.

The following registers are contained in the CPU and connected directlyto the system bus. The CPU has four internal registers each of 16 bits. Input flag 1 bit FGO.

Input Flag 1 bit FGO. A 64-bit processor will generally have 64-bit registers as it deals with 64-bit instructions. IO CPU IO CPU Job3.

Input Register 8 bits. AH is the high and AL is the low bytes of the AX register. Input register 8 bits OUTR.

Output Flag 1 bit IEN. Output register 8 bits FGI. This means the jobs are interleaved as.

Describe the Man in a Box concept of a CPU. Output Flag 1 bit IEN. The following registers are contained in the processor and connected directly to the system bus.

This nomenclature is also appropriate to the BX CX and DX registers. Interrupt enable 1 bit Keystroke input from the. Output Flag 1 bit IEN.

4 b Use the statements A B C and D to complete the description of how the fetch-execute cycle handles an interrupt. Output Register 8 bits FGI. What was the first CPU to use the four AX-DX general purpose registers.

Interrupt Enable 1 bit Keystroke input from the teletype and printer output to the teletype are controlled by the IO module. The first four AX BX CX and DX are common use registers and can also be used as 8 bit registers if used in such a way it is essential to refer to them such as. Interrupt Enable 1 bit Keystroke input from the Teletype and output to the printer are controlled by the IO module.

Output flag 1 bit IEN. Input Flag 1 bit FGO. The teletype is able to encode an alphanumeric symbol to an 8-bit word and decode an 8-bit word into an alphanumeric symbol.

Input flag 1 bit FGO. Modern CPU architectures tends to use more GPR so that register-to-register addressing can be used more which is comparatively faster than other addressing modes. Each register performs a specific function.

Output Register 8 bits. Input Register 8 bits. Interrupt Enable 1 bit.

Input register to 0. Input Register 8 bits. 1 describe how the cpu when using the first 4.

Interrupt Enable 1 bit. Consider a computer system that contains an IO module controlling a simple keyboardprinter teletype. The following registers are contained in the CPU and connected directly to the system bus.

The following registers are contained in the processor and con-nected directly to the system bus. Input flag 0 it will be accepted by INPR. For 32-bit processors how does Intel alter the naming scheme of the four general purpose registers.

Input Flag 1 bit. Its content can be accessed by assembly programming. List three distinct types of registers and explain in detail what each one is used for.

The following registers are contained in the CPU and connected directly to the system bus. Input Register 8 bits OUTR. Input Register 8 bits.

HrTr 1-HrHcTc 1-Hr 1-HcTm 09210 1-09209590 1-092 1-0951000 92 684 4 2004 ns Answer 2. This preview shows page 9 - 10 out of 10 pages. Output register 8 bits FGI.

And once 8-bit data enters the INPR then FGI. Output Flag 1 bit IEN. Interrupt Enable 1 bit Keystroke input from the Teletype and output to the printer are controlled by the IO module.

Keystroke input from the teletype and printer output to the teletype are controlled by the IO module. Input flag 1 and the processor transfer data of INPR to AC and change FGI. Input Flag 1 bit FGO.

Input Register 8 bits OUTR. Consider a computer system that contains an IO module controlling a simple keyboard printer Teletype. When CPU wants to store some data in the memory or reads the data from.

Output Flag 1 bit IEN. The manipulated data is then written back to the memory via the CPU cache. The following registers are contained in the CPU and connected directly to the system bus.

IO CPU IO CPU A job can execute for one cycle T then it must wait for T before doing another cycle. Consider a computer system that contains an IO module controlling a simple keyboardprinter Teletype. Consider a computer system that contains an IO module controlling a simple keyboard printer Teletype.

Interrupt enable 1 bit Keystroke input from the teletype and printer output to the teletype are controlled by the IO module.

Home Decor Ideas Official Youtube Channel S Pinterest Acount Slide Home Video Home Design Decor Interior Kitchen Aid Kitchen Aid Mixer Kitchen Appliances

Various Instructions Code Formats Addressing Mode Segmentation Direct Address

Meet Zola The Easiest Way To Plan Your Wedding And Register Start With A Free Gorgeous Wedding Plan Your Wedding Honeymoon Fund Fit And Flare Wedding Dress

Comments

Post a Comment